<명령어 세트(instruction set)> -> 회사마다 다름

: 특정 CPU를 위해 정의되는 명령어들 집합

- ISA(Instruction Set Architecture) : 명령어 세트 구조

[명령어 세트 설계 시 고려 사항]

- 명령어 형식

- 주소지정 방식

- 연산의 종류

- 데이터 타입

<명령어 종류>

- 산술연산(arithmetic operation) 명령

- 논리연산(logic operation) 명령

- 데이터 처리 및 메모리 연산 명령 : 데이터 입출력, 로드(memory->CPU), 저장(CPU->memory) 실행

- 흐름제어 연산(control flow operation) 명령 : 프로그램 실행순서 바꾸는 명령 실행

<명령어 형식(instruction form)>

- op code(연산코드 필드) : 연산의 동작 지정

- operand(오러팬드 필드) : 연산의 대상, 위치 표시

ex) op code = '+', operand = 3, 5 -> 3+5

- 한 명령어 안에 여러 개의 operand 필드 가능

- op code가 n비트 : 2^n 가지 연산 종류 지정 가능

- operand가 n비트 : 2^n개의 주소 지정 or 2's complement로 데이터 수치 표시 가능

<어셈블리 명령어 설계(가상)>

산술연산 : ADD

accumulator : AC

gp register : B, C, D

1. ADD [y] : AC와 y번지 메모리 값 더해 다시 AC에 저장

2. ADD B, [y] : B 레지스터와 y번지 메모리 값 더해 다시 B에 저장

3. ADD B, C : B,C 레지스터 각각에 저장된 값을 더해 B에 저장

4. ADD B, C, D : C,D 레지스터 각각에 저장된 값을 더해 B에 저장

<주소지정 방식> == addressing mode

: 명령어 형식에 포함된 operand 필드에서 실제 피연산자 찾아내는 방법

- 유효주소(effective address) : 실제 operand 주소. 실제 피연산자가 저장된 메모리 위치

- 간접주소 : 유효주소가 저장된 메모리 위치

산술연산 : INC, ADD

accumulator : AC

Program counter : PC

gp register : B,C

index register : IX

변위값 : d

1. 암시적(implied) 주소지정 방식 : operand없이 연산코드만으로 동작 암시

INC; AC <- AC +. 1

2. 즉치(immediate) 주소지정 방식

ADD B, 90H; B <- B + 90H(Hexa)

3. 직접(direct) 주소지정 방식

ADD B, [1234H]; B <- B + M[1234H]

4. 간접(indirect) 주소지정 방식

ADD B, [[5678H]]; B <- B + [M[5678H]]

5. 레지스터(register) 주소지정 방식

ADD B, C; B <- B + C

6. 레지스터 간접(register indirect) 주소지정 방식

ADD B, [C]; B <- B + M[C]

7. 상대 주소지정 방식(relative addressing mode)

ADD B, [PC+d]; B <- B + M[PC+d]

8. 인덱스 주소지정 방식(indexed addressing mode) : 배열연산에 유리

ADD B, [IX+d]; B <- B + M[IX+d]

<정수의 산술연산>

- 부호없는 양수 : 8bit로 0~255 표시

- 음수 고려 : 첫 비트를 sign비트로 사용

음수 표현은 3가지

1. 부호-크기 영역 표현 : -127 ~ 127

2. 1's complement : -127 ~ 127

3. 2's complement : -128 ~ 127(1's complement + 1)

- 2's complement 많이 쓰는 이유 : 음수를 하나 더 표현할 수 있다

<사칙연산>

[가산기]

- 비트 수 자리만큼 full adder로 구성

- 보수화기 추가해 2's complement로 표현된 두 수 더함(뺼셈을 덧셈처럼 하기 위해서)

[곱셈기, 나눗셈기]

- 보수화기, 시프트 레이즈터, 가산기 등으로 구성

- 반복적인 시프트 동작과 덧셈,뺄셈 동작

ex) 2진수 오른쪽으로 1bit shift하면 /2, 왼쪽으로 1bit shift하면 *2 효과

[실수]

정수, 소수로 구성

[10진수 -> 2진수]

: 정수부, 소수부 나눠서 변환

[고정소수점, 부동소수점]

- 고정소수점(fixed point) : 소수점 위치 고정되고 정수부, 소수부로 표시

- 부동소수점(floating point) : 소수점 위치 이동시켜 지수로 나타냄. 넓은 범위 수 나타낼 수 있지만 연산속도 느려 별도의 보조프로세서 사용

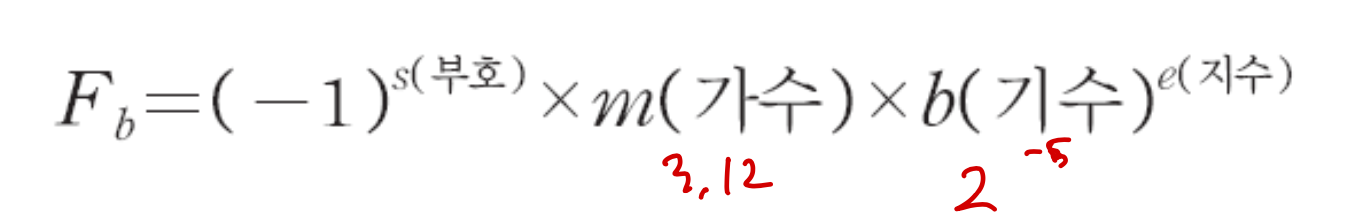

[부동소수점 표현 방식]

: 가수부 + 지수부

- 부호(sign) : 양수 : 0, 음수 : 1

- 가수부(mantissa) : 유효숫자로 정수부, 소수부 표시

- 지수부(exponent) : 소수점 위치 지정

- 기수(base) : 진법

- 유효숫자(significant figure) : 자릿수를 나타내는 숫자 0을 제외한 나머지 신뢰할 수 있는 숫자(10진수에서 유효숫자 : 0~9, 2진수에서 유효숫자 : 0,1)

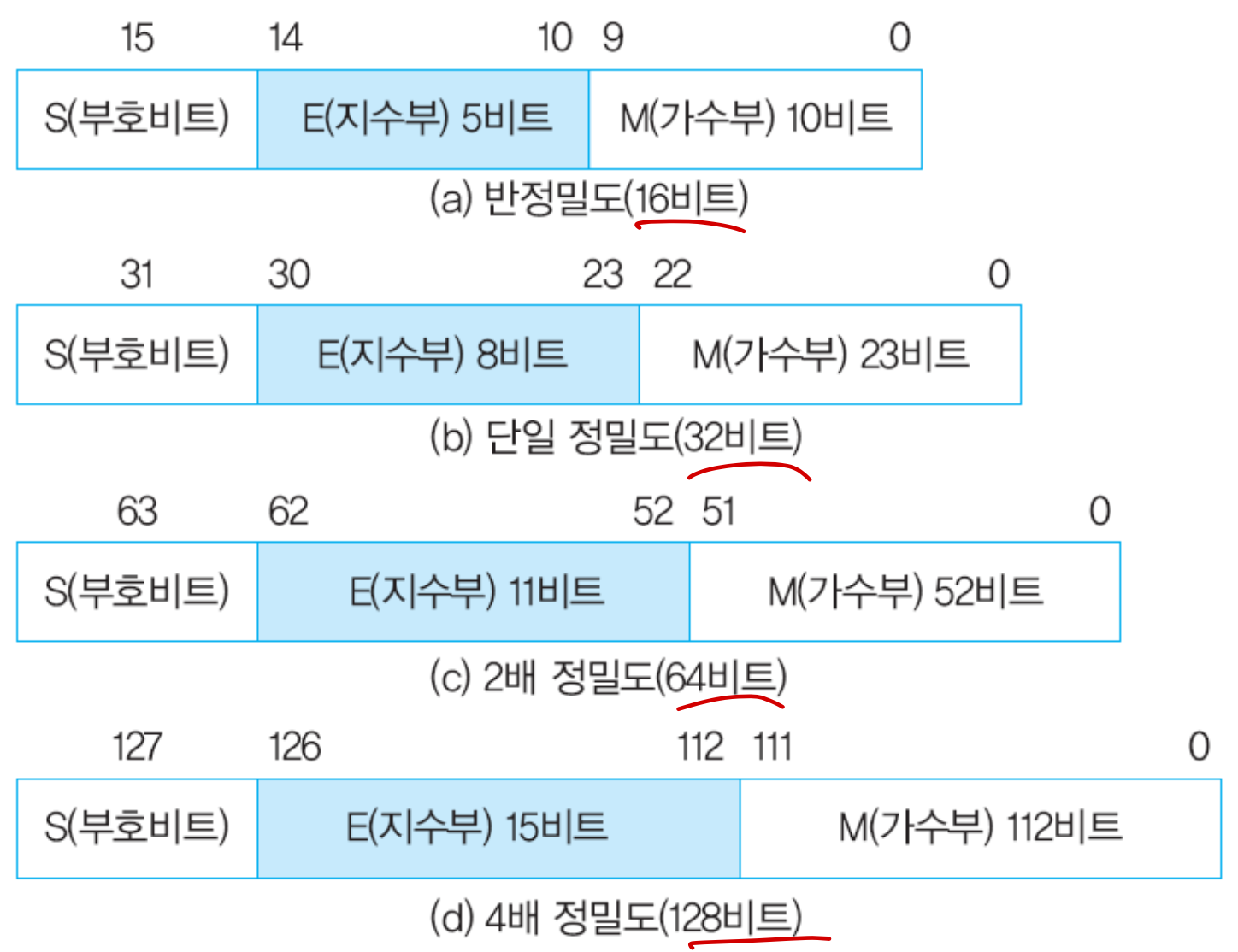

- IEEE 754 표준 2진 부동소수점 형식

<지수 바이어스(exponent bias)>

: 지수에 일정 기준 값을 더해 부호가 필요없는 영역으로 옮겨 저장(2's complement로 표현하면 크기 비교 어려움)

- k bit 지수 부 -> s^(k-1)-1 bias된 지수로 저장

ex) 8bit 지수부이면 +127

<정규화(normalized) 형식>

: 소수점 위치에 따라 여러 가지로 표현되므로 통일된 표준 형식 사용

- 소수점 앞에 정수부로 항상 '1'이 오도록 정규화

- 정수부를 '1'로 초기화(모든 bit가 0이면 0으로 정의)

- 가수부에서 소수부만 저장(정수부는 1이니까)

ex)

-1.1101 x 2^4를 32bit 2진 부동소수점 형식으로 저장하고 16진수로 표현

- 음수니까 부호 비트는 1

- 지수부는 4(00000100) + 127(01111111) = 131(10000011)

- 가수부는 -1.1101 x 2^4에서 1101이 맨 앞에 옴(정수부 1이니까)

- 16진수로 표현하면 0xC1E80000

<논리 및 시프트 연산>

: NOT, AND, OR, XOR, shift register를 이용한 비트 열 이동

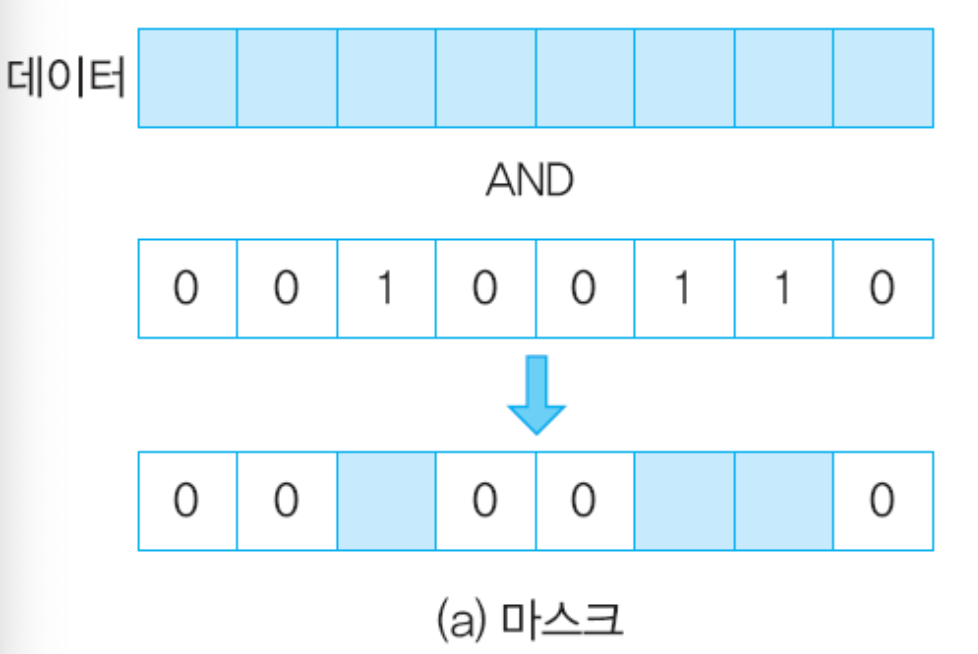

[mask 연산]

: AND 연산으로 원하는 위치의 비트만 통과

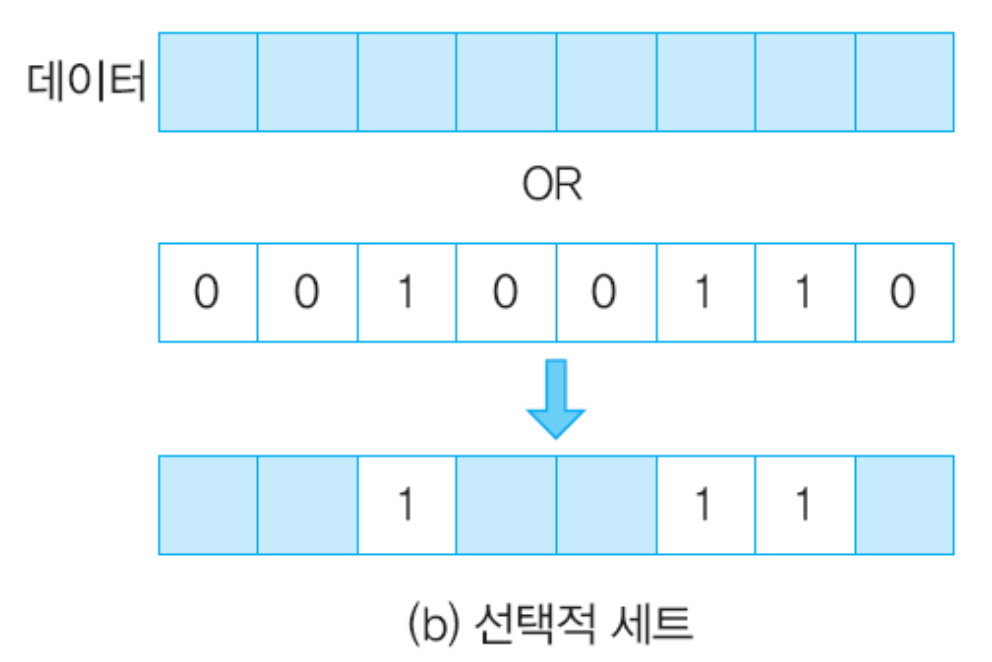

[선택적 세트(selective set)연산]

: OR 연산으로 원하는 위치의 비트만 1로 세트

[삽입(insert) 연산]

: AND 연산으로 원하지 않는 위치 비트 지우고 OR 연산으로 다른 데이터 값으로 교체

* 자릿 수가 0 or 1인지 확인하는 법

=> 연산 후에 맨 오른쪽 비트로 shift해준다

[비교(compare) 연산]

: XOR 연산으로 다른 값을 갖는 위치만 1

[선택적 보수(selective complement) 연산]

: XOR 연산으로 원하는 위치의 비트만 1's complement로

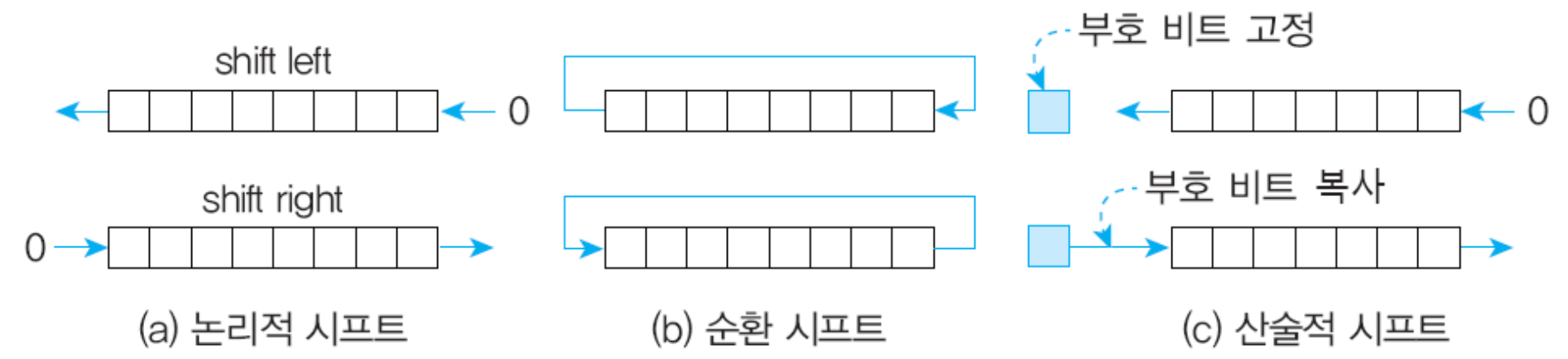

<시프트 연산>

[논리적 시프트(logical shift) 연산]

- 부호 고려하지 않음

- shift register들이 좌우로 1bit씩 이동

- 곱셈 or 나눗셈에 적용

[순환 시프트(circular shift) 연산]

- 부호 고려하지 않음

- shift register 비트들이 회전해 다시 반대쪽 입력으로 들어감

- 직렬 데이터 비트 전송에 사용

[산술적 시프트(arithmetic shift) 연산]

- 부호 비트 제외한 나머지 비트들 좌우 이동

- 2's complement 표현에서는 오른쪽으로 shift할 때는 부호 비트가 우측으로 복사

- 부호 고려한 비트 확장에 사용

'Computer > 컴퓨터구조 운영체제' 카테고리의 다른 글

| 4.2 병렬계산 (0) | 2022.04.18 |

|---|---|

| 4.1 CPU 명령어 사이클 (0) | 2022.04.18 |

| 3.4 연산장치 (0) | 2022.04.05 |

| 3.3 레지스터 (0) | 2022.04.05 |

| 3.2 보조프로세서 (0) | 2022.04.05 |